## Advanced Converter Systems for High Temperature Environments

#### **Burak Ozpineci**

Email: ozpinecib@ornl.gov Phone: 865-946-1329 Organization: Oak Ridge National Laboratory

> Principal Investigator: Leon Tolbert Agreement: 13270

Project Duration: FY06 to FY08 FY08 Funding: \$802K

#### DOE Vehicle Technologies Program Overview of DOE VTP APEEM R&D

North Marriott Hotel and Conference Center Bethesda, Maryland

February 28, 2008

Managed by UT-Battelle for the Department of Energy

National Transportation Research Center

# **Purpose of Work**

- Demonstrate 55 kW DC-DC converter that is capable of operating at 8 kW/kg and 11 kW/l with efficiency greater than 98%.

- Demonstrate high temperature gate drive capable of driving SiC FET (JFET or MOSFET) in a 200°C ambient.

- Demonstrate high temperature packaging of higher power SiC module (multiple devices in parallel to achieve current ratings required).

# **Technical Approach**

# Develop

- High power bidirectional DC-DC converter with minimal inductance.

- High temperature packaging of silicon carbide (SiC) FETs so that they can operate at 200°C.

- High temperature SOI gate drives that can operate at an ambient of 200°C.

# **Responses to Reviewers' Comments**

#### • Comment: "High temperature gate driver work needed"

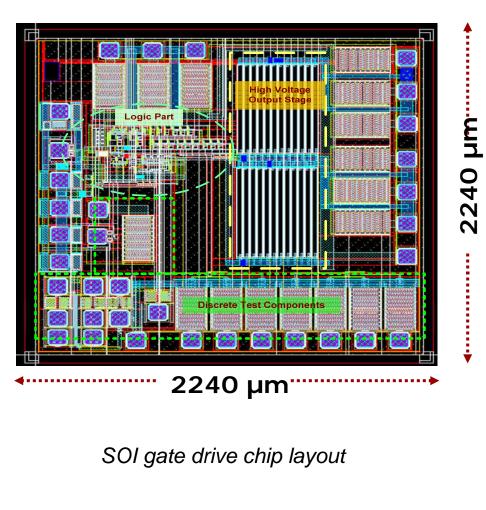

Response: High temperature gate driver work using silicon on insulator technology has been conducted. The first generation gate driver has been designed built and tested. The second generation design is being fabricated and tested in the FY08 program.

Comment: "Needs significant emphasis on reliable high temperature packaging"

Response: High temperature packaging work was initiated in FY07 and has continued into FY08. Significant progress has been made in obtaining reliable packaging up to  $200^{\circ}$ C.

# **Barriers**

#### • VTP Related Challenges

- Targets for the coolant loop are moving toward 105°C for liquid coolant loops.

- Manufacturers interested in eliminating coolant loops and using air cooling which requires converters capable of operating at high temperature.

#### • Technology Related Challenges

- Commercial release of SiC switching devices (JFETs and MOSFETs) has been slower than expected which has hindered ability to obtain sufficient quantities for high power demonstrations.

- First demonstration of high power gate drives in SOI on a single chip. Expected to require a few iterations to find all issues.

- Availability of high voltage, high temperature capacitors with large capacitance values.

# **Technical Approach for FY08**

- Complete assembly of 55 kW bidirectional DC-DC converter

- Conduct functionality and efficiency tests (converter to provide 30 kW continuous and 55 kW for 18 seconds)

- Replace film capacitors with high temperature capacitors if available

- Design and simulate second generation high temperature gate drive in SOI

- Incorporate bootstrap capacitor

- Add power supply to chip

- Increase peak current charging capacity

- Fabricate and test gate drive chip for functionality over wide temperature range

- Obtain SiC JFETs or MOSFETs from vendors

- Demonstrate high temperature packaging and capability of integrating several dies into a single module

# **Technical Approach - Uniqueness**

- A high-temperature multilevel bidirectional DC-DC converter that can boost voltage by a factor of 3X is being developed.

- Reduce size of boost converter and enable higher temperature operation (up to 200°C).

- Converter is expected to have high efficiency because of low switching frequency.

- High temperature gate drive with minimal volume.

# **Technical Accomplishments through FY07**

- SOI high temperature gate drive fabricated.

- High temperature PCB test board designed and fabricated

- Chip tested from -40°C to 200°C with a SiC MOSFET.

8 Managed by UT-Battelle for the Department of Energy

#### **Technical Accomplishments through FY07 (cont.)**

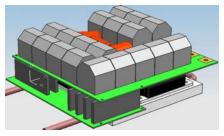

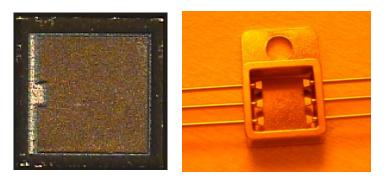

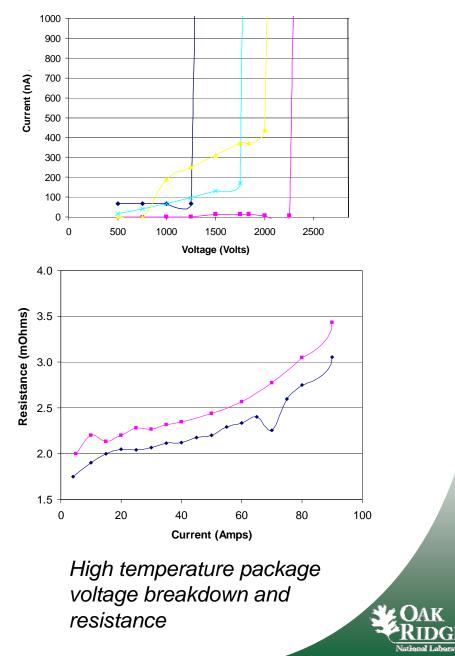

- High temperature packaging of SiC JFETs

- 2 JFETs/package in parallel arrangement

- Silver filled polyimide adhesive used for die attach material

SiC JFET and demonstration package

9 Managed by UT-Battelle for the Department of Energy

#### **Technical Accomplishments through FY07 (cont.)**

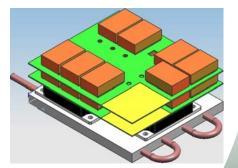

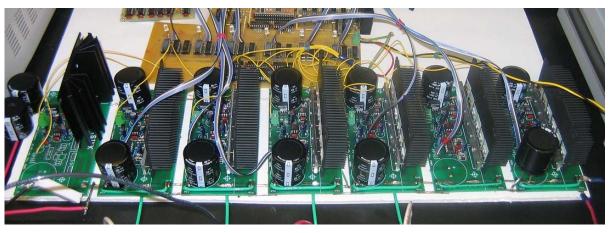

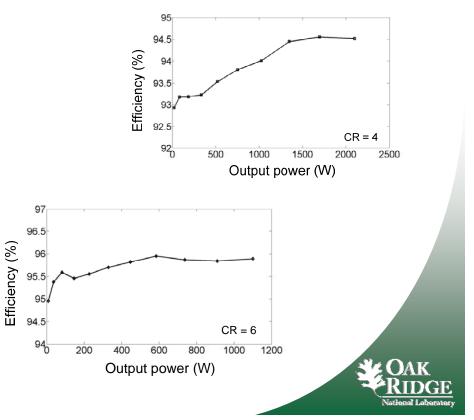

#### 5 kW Multilevel Modular Capacitor Clamped Converter (MMCCC)

- Designed, fabricated, tested

- Has redundant levels, bypass capability for faulty cell

- Bidirectional capability

- Efficiency in 95 to 96% range for voltage ratio of 6, less with lower voltage ratios

# **Timeline for FY08**

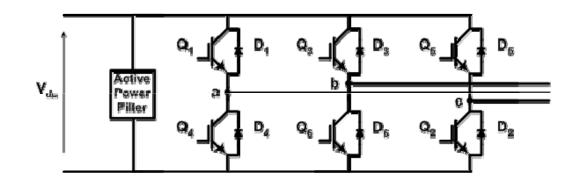

| 2007<br>Oct                                                                  | Nov                                               | Dec | 2008<br>Jan | Feb | Mar                          | Apr | Мау | Jun                | Jul | Aug             | Sep             |  |

|------------------------------------------------------------------------------|---------------------------------------------------|-----|-------------|-----|------------------------------|-----|-----|--------------------|-----|-----------------|-----------------|--|

| Desigr                                                                       | Design and fabricate second generation gate drive |     |             |     |                              |     |     |                    |     |                 |                 |  |

|                                                                              |                                                   |     |             |     |                              |     |     | Test of gate drive |     |                 | Final<br>Report |  |

| Final fabrication and test of 55 kW 200 V / 600 V multilevel DC-DC converter |                                                   |     |             |     |                              |     |     |                    |     | Final<br>Report |                 |  |

|                                                                              |                                                   |     |             |     | Package SiC JFETs for module |     |     |                    |     |                 |                 |  |

No decision point because work is complete at the end of FY08.

11 Managed by UT-Battelle for the Department of Energy

# **Technical Accomplishments FY08**

- A second generation highly integrated SOI chip has been designed and fabricated. Initial testing starts in March.

- A 55 kW DC-DC converter has been assembled and testing is in progress to demonstrate high efficiency capabilities.

# **Technology Transfer**

General Motors Advanced Technology Vehicles and U.S. Air Force Research Laboratory have expressed interest in high temperature gate drives and packaging. After testing 2<sup>nd</sup> generation gate drives, some will be sent to both organizations for their evaluation and/or use.

## **Future Work**

• Project is complete at the end of FY08.

14 Managed by UT-Battelle for the Department of Energy

# Summary

- A high efficiency, bi-directional DC-DC converter has been developed.

- Highly integrated, high temperature SOI gate drives and high temperature packaging of SiC devices have been fabricated and tested.

- High temperature gate drives and packaging have attracted interest from some companies and other federal organizations. We have shared some of our devices with them already and will continue to collaborate on future work.

# **Publications, Presentations, Patents**

- M. Shen, F. Z. Peng, L. M. Tolbert, "Multi-Level DC/DC Power Conversion System with Multiple DC Sources," *IEEE Power Electronics Specialist Conference*, Orlando, Florida, USA, June 17-21, 2007, pp. 2008-2014.

- M. Huque, R. Vijayaraghavan, M. Zhang, B. Blalock, L. Tolbert, S. Islam, "An SOI-based High-Voltage, High-Temperature Gate-Driver for SiC JFET," *IEEE Power Electronics Specialist Conference*, Orlando, Florida, USA, June 17-21, 2007, pp. 1491-1495.

- K. Vanam, F. Barlow, B. Ozpineci, L. D. Marlino, M. S. Chinthavali, L. M. Tolbert, and A. Elshabini, "High Temperature SiC Packaging for HEV Traction Applications," *IMAPS 2007 - International Symposium on Microelectronics*, San Jose, California, Nov. 11-15, 2007.

- L. M. Tolbert, H. Zhang, M. S. Chinthavali, B. Ozpineci, "SiC-based Power Converters for High Temperature Applications," *Materials Science Forum*, vols. 556-557, 2007, pp. 965-970.

- F. Khan, L. M. Tolbert, "A 5-kW Multilevel DC-DC Converter for Hybrid Electric and Fuel Cell Automotive Applications," *IEEE Industry Applications Society Annual Meeting*, September 23-27, 2007, New Orleans, Louisiana.

17 Managed by UT-Battelle for the Department of Energy

## An Active Filter Approach to the **Reduction of the DC Link Capacitor**

Phone: 865-946-1329 Organization: Oak Ridge National Laboratory

Agreement: 13268

Project Duration: FY08 to FY09 FY08 Funding: \$158K

**DOE Vehicle Technologies Program Overview of DOE VTP APEEM R&D**

North Marriott Hotel and Conference Center Bethesda, Maryland

February 28, 2008

Managed by UT-Battelle for the Department of Energy

National Transportation

**Research Center**

This presentation does not contain any proprietary or confidential information

#### **Purpose of Work**

- The objective of this project is to replace the bulky DC link capacitor with much smaller size active filter that imitates what a DC link capacitor does

- The weight and volume of the traction inverter will be reduced while the reliability and lifetime of the inverter will be increased

- The active filter is expected to weigh half as much as the DC link capacitor and occupy less than half the space

2 Managed by UT-Battelle for the Department of Energy

#### **Response to Reviewer's Comments**

# This is a new start in FY08; no previous review has been conducted

# **Barriers**

#### • VTP Related Challenges

#### DC link capacitor problems

- Size (35-40% of the volume and 23% of the weight of an inverter)

- Cost (23% of an inverter)

- Limited high temperature operation capability

- Separate cooling

#### Technology Related Challenges

The possibility of extremely high sampling and switching frequency requirement

# **Technical Approach for FY08**

- Task 1 Establish performance requirements for an active filter

- Task 2 Simulate an active filter that can replace a DC link capacitor for a traction inverter

- Task 3 Assess simulation results

# **Technical Approach - Uniqueness**

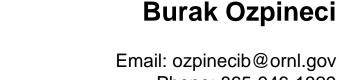

- An active filter with much smaller capacitor and inductor can be used in the DC link together with semiconductor switches to replace the DC link capacitor

- Impacts

- Reduced size and cost

- May provide more cost-effective solution for high temperature operation

# **Timeline for FY08**

# **Technical Accomplishments for FY08**

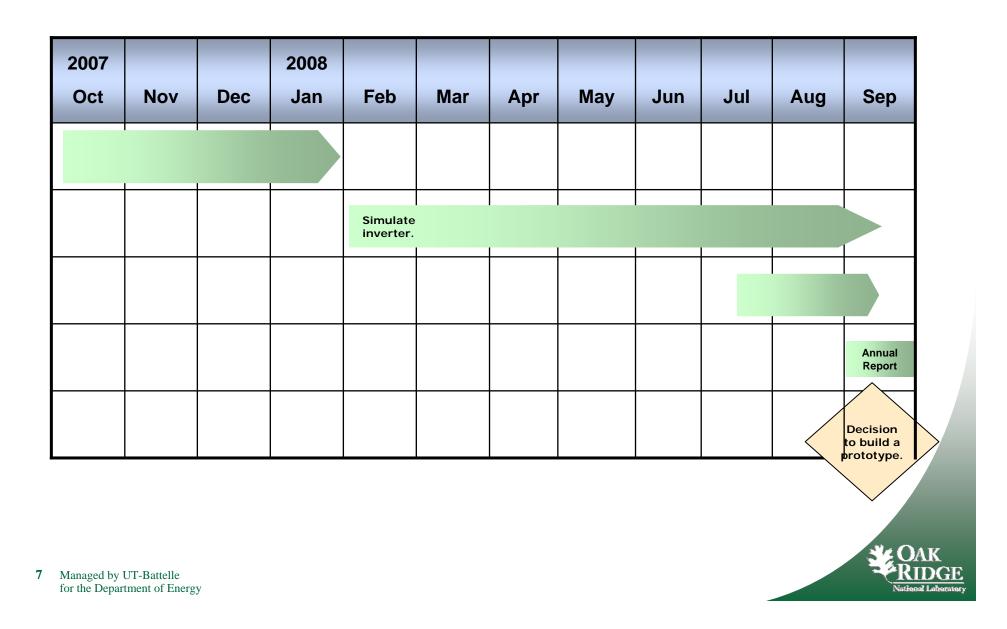

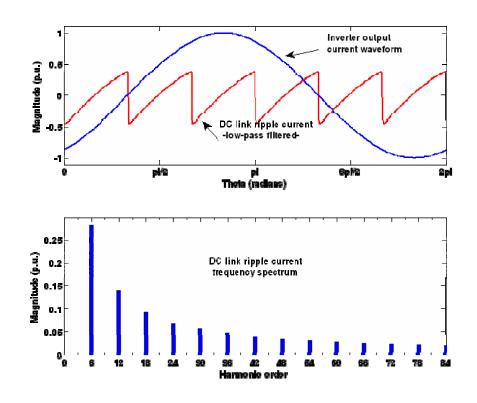

Simulation model of a traction drive system was used to establish the performance requirements for an active power filter.

8

Filtering Effect Demonstration

# **Technical Accomplishments for FY08**

- The input current to a three-phase inverter contains distinct high frequency and low frequency components.

- The high frequency components can be filtered using a small high-frequency capacitor in the DC link in parallel with the DC link capacitor.

i.e. increasing the switching frequency of an inverter does not reduce the size of the bulky DC link capacitor.

• The purpose of the main DC link capacitor is to filter the low order harmonics with a fundamental of six times the output frequency.

## **Technical Accomplishments for FY08**

• The active filter should be able to eliminate the same low order harmonics by injecting these harmonics into the DC link.

**10** Managed by UT-Battelle for the Department of Energy

# **Technology Transfer**

Industrial representatives have expressed interest in this work. Talks with them will continue after the feasibility of the concept is demonstrated.

# **Future Work**

#### • FY09

Design and build an active power filter module. Test the module in a 55 kW inverter replacing the DC link capacitor.

# Summary

- An active filter is being developed to replace the bulky dc link capacitor and weigh half as much as the typical capacitor.

- The first year of the project includes establishment of requirements for the active filter and its simulation. The active filter will be built as a module and tested in the second year to replace a dc link capacitor.

# **Publications, Presentation, Patents**

None

14 Managed by UT-Battelle for the Department of Energy

Managed by UT-Battelle for the Department of Energy

# Wide Bandgap Materials

#### **Burak Ozpineci**

Email: ozpinecib@ornl.gov Phone: 865-946-1329 Organization: Oak Ridge National Laboratory

Principal Investigator: Madhu Chinthavali Agreement: 13259

> Project Duration: FY01 to FY10 FY08 Funding: \$432K

DOE Vehicle Technologies Program Overview of DOE VTP APEEM R&D

North Marriott Hotel and Conference Center Bethesda, Maryland

February 28, 2008

Managed by UT-Battelle for the Department of Energy

This presentation does not contain any proprietary or confidential information

### **Purpose of Work**

- Maintain knowledge base of wide bandgap (WBG) material-based power devices

- Continue cognizance of literature

- Obtain and test sample and pre-commercial WBG-based devices from various manufacturers

- Characterize and model them for comparison purposes

- Develop novel inverter/converter designs, packaging, and thermal control concepts that utilize attributes of the WBG-based power devices attributes

#### **Responses to Reviewers' Comments**

• Comment: "Would like to see more actual data of inverter performance rather than simulations."

Response: Inverter testing using SiC devices was initiated in FY07 and performance of the inverter was documented for all SiC and hybrid Si/SiC designs was reported.

• Comments:

"One of the best projects reported at APEEM review....need to do more"

"Good analysis, and report, valuable information"

# **Barriers**

# **VTP Related Challenges**

- Need for reduced size and weight of the power converters and their cooling systems

- Need for increased efficiency of power converters

- Produce power converters capable of operating in high temperature environments

## **Technology Related Challenges**

- Acquiring new prototype devices

- Developing appropriate test fixtures for new high temperature, high speed device evaluations

# **Technical Approach for FY08**

- Acquire, test, and characterize newer technology WBG power devices

- Static characteristic tests

- Dynamic characteristic tests

- Behavioral modeling

- Determine converter concepts that make best use of the attributes of WBG-based power devices

- Design and develop circuits

- Model and simulate novel converter designs and thermal control concepts

# **Technical Approach - Uniqueness**

- Evaluation of device performance provides insight into the development of the maturing high temperature device technology.

- New high temperature, high frequency gate drivers, and passive components need to be developed to evaluate device performance.

- Technological breakthroughs packaging concepts, thermal requirements for HEVs, PHEVs, and FCVs.

- The impact will be smaller automotive power converters that can operate at higher temperatures and efficiencies.

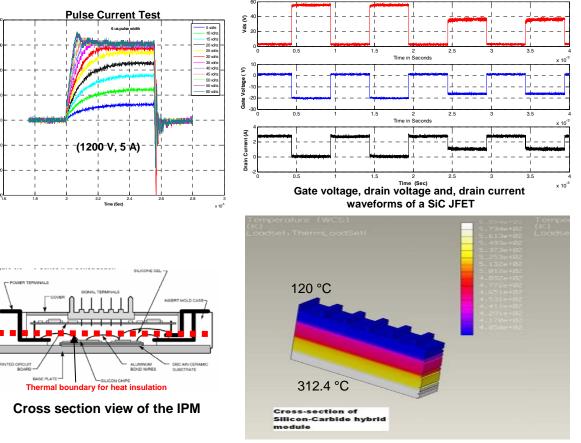

### **Technical Accomplishments through FY07**

- Tested, characterized, and modeled SiC Schottky diodes, JFETs, and MOSFETs.

- A hybrid package was developed and modeled.

- Circuits were developed to study the fault current limiting capability of SiC devices.

- An inverter loss model was successfully integrated into the drive train model in PSAT.

FEA results for the SiC hybrid IPMs heat flow analyses

# **Timeline for FY08**

| 2007<br>Oct                                                                                | Nov | Dec | 2008<br>Jan | Feb | Mar | Apr | Мау | Jun | Jul | Aug | Sep              |

|--------------------------------------------------------------------------------------------|-----|-----|-------------|-----|-----|-----|-----|-----|-----|-----|------------------|

| Acquire, test, and characterize newer technology SiC power devices                         |     |     |             |     |     |     |     |     |     |     |                  |

| Determine novel inverter/converter designs, packaging, and thermal control for WBG devices |     |     |             |     |     |     |     |     |     |     |                  |

|                                                                                            |     |     |             |     |     |     |     |     |     |     |                  |

|                                                                                            |     |     |             |     |     |     |     |     |     |     | Annual<br>Report |

**Decision point discussion:** Based on the merit of the new concepts a decision will be made if any of them have to be developed further.

# **Technical Accomplishments FY08**

#### **Demonstrated performance of**

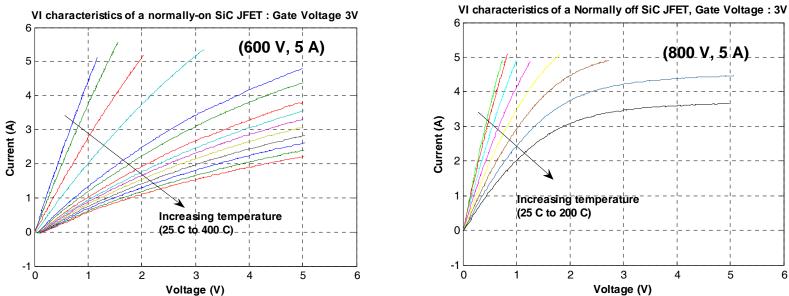

- 600 V, 5 A high-temperature packaged normally-on SiC JFET at 400°C. On-state resistance increased from 0.25 Ω at 25 °C to 2.5 Ω at 400°C.

- 800 V, 5 A normally-off SiC JFET( first normally-off SiC JFET) prototype device was tested. On-state resistance increased from 0.15 Ω at 25°C to 0.88 Ω at 200°C at gate voltage of 3 V.

# Technical Accomplishments FY08 (Cont'd)

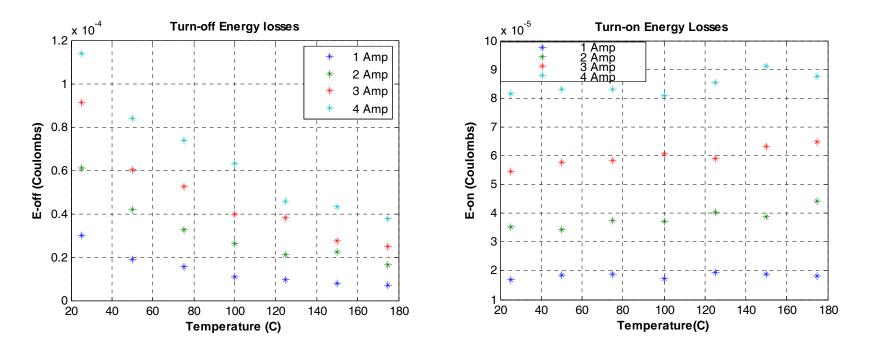

Dynamic characteristics of a normally-on 600 V, 5 A SiC JFET

# **Technology Transfer**

ORNL has collaborated with (GM, Delphi) and device manufacturers (Cree, Semisouth, Velox) in sharing the knowledge base of device test results and models.

# **Future Work**

#### • FY09 and FY10

- Continue to acquire, test, and characterize new devices as they become available

- Develop new concepts as merited

# Summary

- Tested and characterized two SiC JFETs

- Actively developing new concepts to improve high temperature inverter designs, thermal control systems, and packaging

# **Publications, Presentation, Patents**

- 1. L. M. Tolbert, H. Zhang, M. S. Chinthavali, B. Ozpineci, "SiC-based Power Converters for High Temperature Applications," *Materials Science Forum*, vols. 556-557, 2007, pp. 965-970.

- 2. B. Ozpineci, M. Chinthavali, L. M. Tolbert, A. Kashyap, and H. A. Mantooth "A 55 kW Three-Phase Inverter with Si IGBTs and SiC Schottky Diodes," *IEEE Transactions on Industry Applications* (in press).

Managed by UT-Battelle for the Department of Energy