## Design and Development of a Low Cost, Manufacturable High Voltage Power Module for Energy Storage Systems

Phase I SBIR

September 27, 2012

Brandon Passmore, PhD

Sr. Electronics Packaging Research Engineer

Email: bpassmo@apei.net

### **Acknowledgements**

I would like to thank Dr. Imre

Gyuk of the DOE Energy Storage

Systems Program and Dr. Stan

Atcitty for technical support

I would also like to thank

### APEI, Inc. Manufacturing Facilities

- APEI, Inc. Class

1000 Manufacturing

- ISO 9001 Certified

- AS 9100 Certified

### **SBIR Program Goals**

Design and develop a high performance, high voltage SiC multi-chip power module (MCPM) that targets energy storage applications

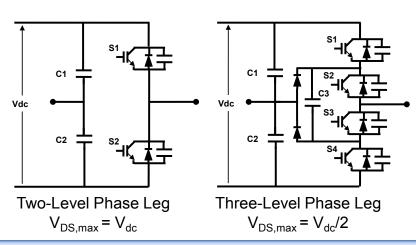

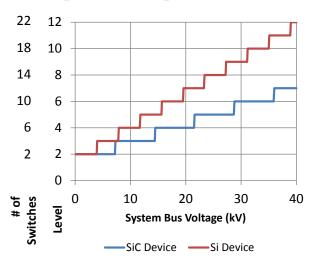

# HV SiC Power Modules Reduce Energy Storage System Size and Complexity

Multi-level converters reduce voltage stress on power devices:

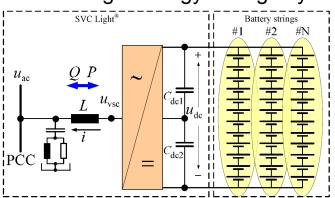

#### ABB's SVC Light energy storage system<sup>1</sup>

#### Comparison of solutions for a 11 kV 600 kW ESS

| Tachnology |                      | Relative            |       |              |            |           |

|------------|----------------------|---------------------|-------|--------------|------------|-----------|

| Technology | $V_{_{\mathrm{BD}}}$ | T <sub>i</sub> (°C) | Level | No. Switches | Freq. (Hz) | Size/Mass |

| Si Device  | 6.5 kV               | 125                 | 10    | 54           | 900        | (28x)     |

| SiC Device | 12 kV                | 175                 | 6     | 30           | 18000      | 1.4x      |

| SiC Device | 12 kV                | 225                 | 6     | 30           | 25000      | 1x        |

<sup>&</sup>lt;sup>1</sup> Wade, N., Taylor, P., Lang, P., Svensson, "Energy Storage for Power Flow Management and Voltage Control on an 11kV UK Distribution Network", 20th International Conference on Electricity Distribution, June 2009.

### Other Targeted Applications

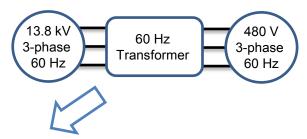

#### **Solid State Transformers**

- Replace passive transformers with power electronic converters to reduce size

- Isolation transformer size proportional to frequency

#### **Passive Transformer**

#### Solid State Transformer<sup>2</sup>

#### Comparison of solutions for a 13.8 kV / 480 V 100 kVA substation transformer

| <u> </u>   |                   |                     |       |              |                       |           |                  |

|------------|-------------------|---------------------|-------|--------------|-----------------------|-----------|------------------|

| Technology | Power Electronics |                     |       |              | Isolation Transformer |           |                  |

|            | $V_{BD}$          | T <sub>i</sub> (°C) | Level | No. Switches | Freq. (Hz)            | Mass (kg) | Volume (m³)      |

| Passive    | N/A               | N/A                 | N/A   | N/A          | 60                    | 370       | 0.480            |

| Si Device  | 6.5 kV            | 125                 | 7     | 70           | 1000                  | 35.8      | <b>70×</b> 0.286 |

| SiC Device | 12 kV             | 175                 | 4     | 40           | 17000                 | 10.2      | 0.057            |

| SiC Device | 12 kV             | 225                 | 4     | 40           | 24000                 | 5.32      | 0.014            |

34×

## Existing HV Power Modules vs. Next Generation HV Power Modules

| Existing HV Silicon (Si) Power Modules         | APEI's HV Silicon Carbide (SiC) Power Module Developed in this SBIR Program |  |  |

|------------------------------------------------|-----------------------------------------------------------------------------|--|--|

| Larger volume/weight than desired              | Reduced volume/weight => Simplify system                                    |  |  |

| Limited voltage blocking capability (< 5kV)    | High voltage (> 15 kV) capable                                              |  |  |

| Lower switching frequency                      | Demonstrated high switching frequency                                       |  |  |

| Lower efficiency                               | Higher efficiency due to low conduction losses                              |  |  |

| Requires bulky magnetics and filter capacitors | Small magnetics and filter capacitors                                       |  |  |

| Maximum operation temperature is below < 125°C | High operation temperature > 200°C                                          |  |  |

| Higher thermal resistance                      | Low thermal resistance due to high thermal conductivity of SiC              |  |  |

HV Si Single Switch IGBT Module

6.5 kV / 750 A, 78 in<sup>3</sup>, 1.8 kg

Simply increasing the size of existing Si power modules does not take advantage of the superior properties of SiC

### APEI's SiC Power Module Package Design **Dramatically Improves Performance**

### 800 600 VDS (V) 400 200 -200 100 150 200 250 Time (ns)

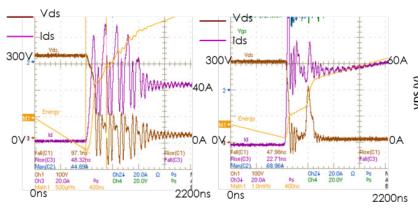

#### MSK (MOSFET)

- $V_{DS} = 300 VDC$

- $I_{DS} = 45 \text{ Amps}$

- Turn On = 47ns

- $E_{op} = 2700 \,\mu\text{J} @ 300 \text{V} / 90 \text{A} \cdot$

#### PowerEx (MOSFET)

- $V_{DS} = 300 VDC$

- $I_{DS} = 60 \text{ Amps}$

- Turn On = 22ns

- $E_{op} = 1600 \, \mu J @ 300 V / 90 A$

#### APEI HT-2000 (MOSFET)

- $V_{DS} = 600 VDC$

- $I_{DS} = 120 \text{ Amps}$

- Turn On = 14ns

- $E_{op} = 70 \, \mu J @ 300 V / 120 A$

- $E_{op} = 300 \, \mu J @ 600 V / 120 A$

### **HT-2000**

- 22 × reduction in turn off losses

- 17% reduction in on-state resistance

- 20% improvement in thermal resistance

- 50% increase in current capability

If the power module design is not optimized, switching losses are exacerbated at high voltage

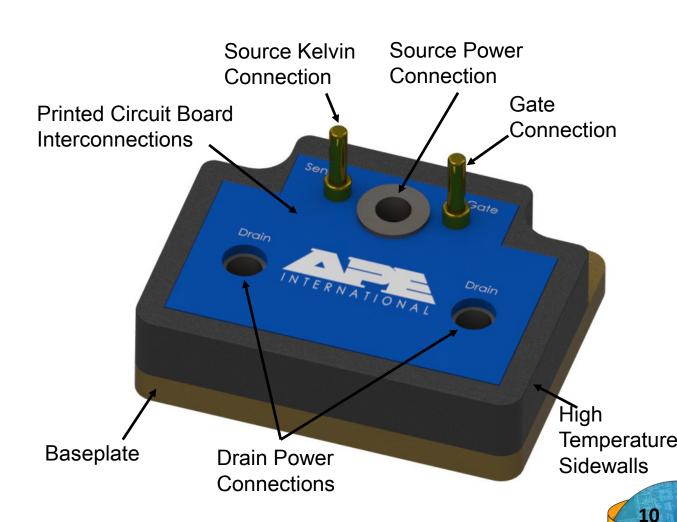

### Key Benefits of APEI's HV MCPM Package Design

- Low junction-to-case thermal resistance

reduces size of cooling system

- Low module parasitics due to wire bondless interconnections => enables high switching frequency

- Ease of manufacturing

- Reliability

- Reworkability

- Reduction in volume/weight

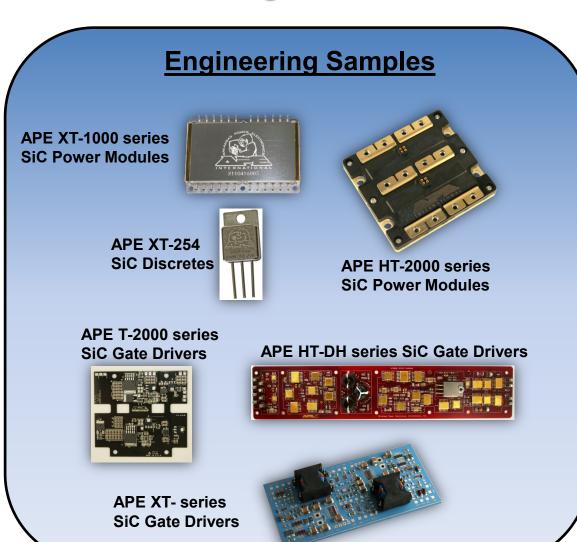

### Discrete Package Will Demonstrate High Performance, HV Package Design

- Device neutral

- High temperature capable (>200°C)

- Low volume

- Low profile

- Wire bondless interconnections

- Improved reliability

- Low resistance and inductance

- Reworkable

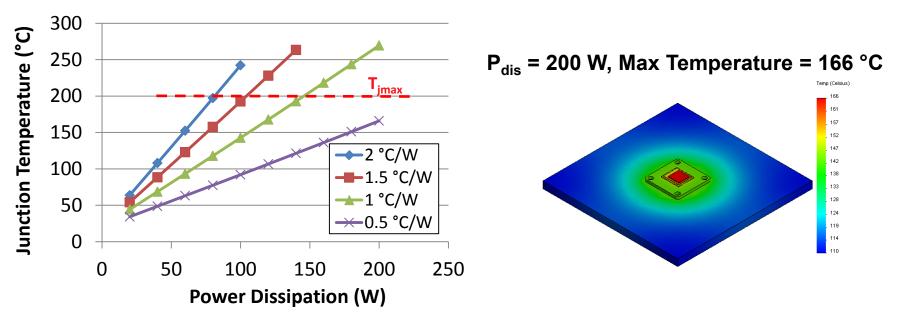

# Discrete Package Thermal Simulations Demonstrate High Thermal Performance for Passive Cooling

- Passive cooling is possible for 200 W of thermal loss due to the low thermal resistance of the package

- Passive cooling significantly simplifies system

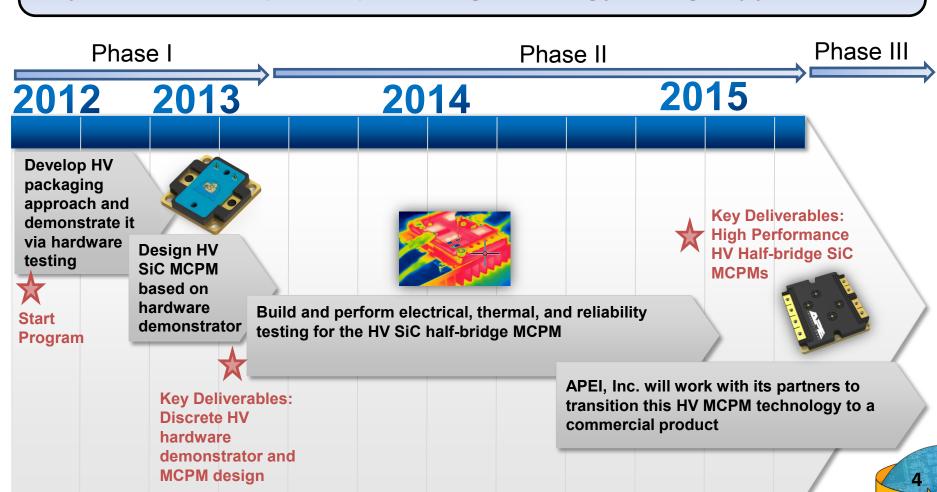

### **Summary**

- Completed HV conceptual discrete package design

- Developed thermal model and confirmed high thermal performance using advanced packaging materials and techniques

- Developed HV design rules

- Targeted applications were identified and analyzed in more detail

### Phase I Future Tasks

- Further investigate ESS applications and work with customers to develop target specs

- Finalize HV discrete package design

- Perform full thermal-mechanical stress analysis on packaging approach

- Fabricate, assemble, and test feasibility of packaging concepts

- Perform high voltage electrical parasitic design and analysis and compare with other conventional packaging approaches

- Half-bridge Power Module Mechanical and thermal Design

Brandon Passmore, Pl <u>bpassmo@apei.net</u> (479) 443-5759