# 6.5 KV SILICON CARBIDE HALF-BRIDGE POWER SWITCH MODULE FOR ENERGY STORAGE SYSTEM APPLICATIONS

Dr. John L. Hostetler

United Silicon Carbide, Inc.

09/27/12

## Acknowledgments

United Silicon Carbide would like to thank <u>Dr. Imre Gyuk</u> of the DOE Energy Storage Program for funding of this project and <u>Dr. Stan Atcitty</u> of SNL for his technical contributions

#### **SBIR DE-FOA-0000628**

- DOE TOPIC NUMBER 8: **High Voltage DC-Link Power Conversion System for Energy Storage Applications**

- Subsection b. Advanced Semiconductor Switches Modules for High Voltage Energy Storage Systems

- PI: Dr. John L. Hostetler

**USCi colleagues:** Dr. Larry Li, Dr. Leonid Fursin, Dr. Petre Alexandrov, Mike Lange, Matt Fox, Guy Moxey, Mari-Anne Gagliardi & Dr. Chris Dries

**USCi Partner:**

## Contents

- Storage Applications

- Role of Power Conversion

- Project Goals & Timeline

- Overall Project Objective

- Impact

- Design Approach

- Reliability Focused

- Device & Half-Bridge Simulations

- Next Steps

- Conclusions

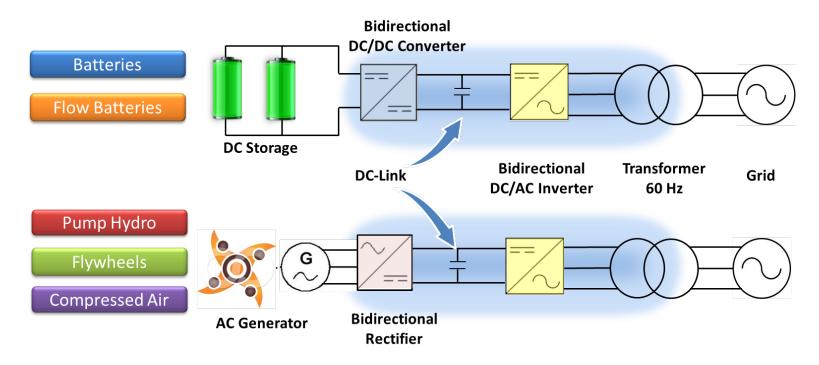

# Storage Applications

Every storage technique involves Power Conversion where the most common interface is a DC-Link.

The Present Cost of Power Conversion Stages is ~30% or Higher of Total System Cost!

## Project Goals & Timeline

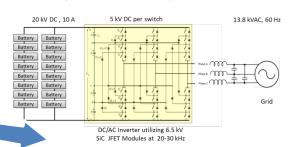

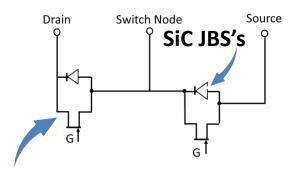

- USCi proposes a 6.5 kV Switch Module that can enable a DC-Link Voltage up to 5 kV using SiC wide bandgap devices:

- Junction Field Effect Transistors (JFETs) and Junction Barrier Schottky Diodes (JBS's)

- Presently, DC-Links reside at ~900 to 1100 V

- Limited by the switch voltage ratings ~ 1200 V Si-IGBTs

- USCi has partnered with Princeton Power Systems to gain critical insight into the impact of a medium voltage switch on inverter systems

- Phase I Design of SiC Power Module and Epitaxial Growth (9 months)

- **Phase II** Fabrication of Power Module and Demonstration of 5 kV DC-link Power Inversion (2 years)

|                  |      | oday N<br>27/12                     | larch 1<br>2013 | 2014            |                                          | 2015       |                  |

|------------------|------|-------------------------------------|-----------------|-----------------|------------------------------------------|------------|------------------|

| Start<br>6/28/12 | Desi | Phase I<br>gn & Epitaxial<br>Growth | Device Fabri    | cation & 5 kV [ | Phase II<br>OC-Link Power Inversion Demo | onstration | Finish<br>1/7/15 |

# Overall Project Objective

- How does higher DC-Link voltage help on the Power Conversion System Level?

- Higher Voltage Means Lower Current

- Losses ~ I<sup>2</sup>R and Switching- More Efficient, Smaller Systems, Less Cooling

- High Operating Frequency—Reduces Magnetics Drastically

- Reduced Footprint, Balance-of-System, and Cost

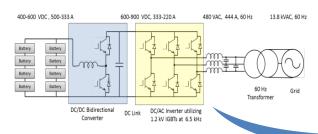

#### **Si-IGBTs**

2 level Inverter

900 V DC-Link

I ~ 300 A/switch

f < 10 kHz</pre>

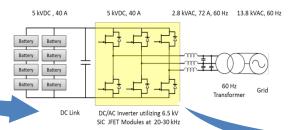

#### 6.5 KV SiC-JFETs

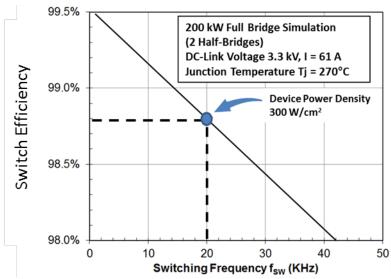

2 level Inverter 5 kV DC-Link I ~40 A/switch f >20 kHz Next Generation Topologies

### **SiC-JFETs**

5 level Inverter 20 kV DC-Link I ~40 A/switch f >20 kHz

# Impact of an all SiC Power Module on Systems

- How does a 6.5 kV SiC Switch Module Impact Storage Systems?

- Costs and Efficiency of Power Conversion Stages

| Parameter                    | Improvement over Si-IGBTs       | Comment                                                           |  |

|------------------------------|---------------------------------|-------------------------------------------------------------------|--|

| System Efficiency            | 1.5-2.0% (~96 to 98%)           | JFETs & JBSs both contribute to efficiency improvements of module |  |

| Switch Frequency             | 2-5 X (<10 kHz to > 20 kHz)     | Greatly Impacts Magnetics                                         |  |

| Operating Current            | X 10 Reduction (~400 A to 40 A) | Greatly Impacts Magnetics & BoS                                   |  |

| <b>Operation Temperature</b> | 1.5 X (150 C to 250 C)          | Reduces Cooling Complexity                                        |  |

# Why a Normally-off SiC JFET?

| Switch type >            | Norm Off                | SIC MOSFET  | SiC Bipolar     | Si IGBT Stack |  |

|--------------------------|-------------------------|-------------|-----------------|---------------|--|

| Property                 | SiC JFET                | SIC WIOSFET | SIC Bipolai     |               |  |

| kV                       | >>6.5 kV                | >>6.5 kV    | >>>6.5 kV       | <6.5 kV       |  |

| Switching speed          | >20 kHz                 | >20 kHz     | <20 kHz         | <5 kHz        |  |

| <b>Switching Loss</b>    | 1X                      | 1X          | ~5X             | ~5X           |  |

| <b>Driver Complexity</b> | Simple                  | Simple      | Complex         | Moderate      |  |

| Operational Tj           | >250°C                  | 150°C       | >250°C          | 150°C         |  |

|                          | No MOS Gate -<br>Robust | MOS Gate -  | V drift (BPD) - |               |  |

| Reliability              |                         | Reliability | Reliability     | Robust        |  |

|                          |                         | Concern     | Concern         |               |  |

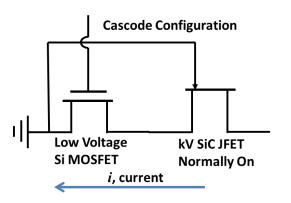

- Cascode Configuration can utilize <u>normally-on</u>

SiC JFETS Very attractive option

- But is limited in operation temperature by the Si MOSFET

- USCi targets high temperature operation to reduce cooling needs -> SiC Normally-off JFET

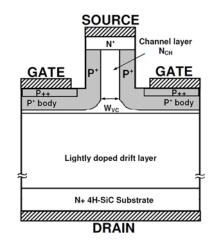

# JFET Design Approach

### Design Focus on Reliability

- Utilize only N-type 4H-SiC Material for all devices in the module

- Unipolar SiC devices more mature than bipolar - not sensitive to Basal Plane Defects

- No MOS Gate

- High Mobility N-channel

- Modest Current Densities keep heat generation low (50 A/cm²)

- Less Stress on Packaging

- Existing SiC Schottky Diode Market Proof of N-type SiC Material Reliability

#### Normally - Off N-type Vertical JFET

SiC JFET's

**Half-Bridge Module**

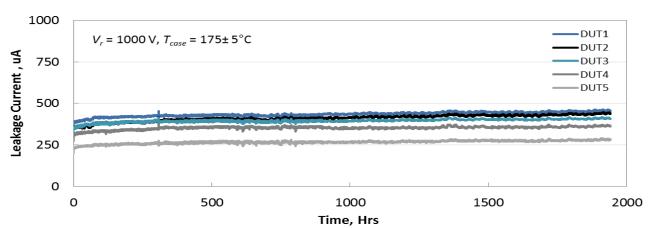

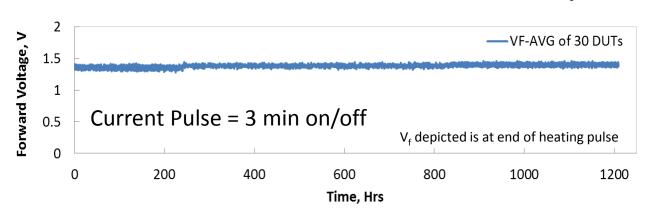

# USCi Schottky Reliability N-type Unipolar Epitaxy

■ High Temperature Reverse Bias,  $T_{case} = 175$ °C

1200 V, 10 A Junction Barrier Schottky Diode TO-220

■ Intermittent Operation Lifetime  $\Delta T_j = 100$ °C

# 6.5 kV Half-Bridge Expected Performance

**Parameter**

**Max DC-Link Voltage**

**Max Current**

Target Ron (RT)

**Switching Speed**

**Max Ambient Temp**

**Max Junction Temp**

**Target**

~ 5 kV

61 A

33 m $\Omega$

~20 kHz

~100°C

~270°C

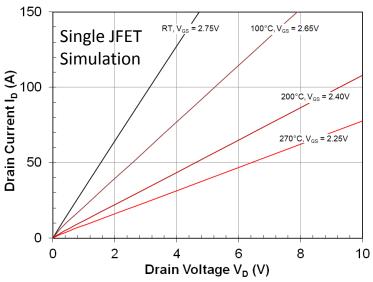

- Full Device Simulation using TCAD

Sentaurus

- Device Simulation Complete

- Packaging Simulation in Progress

- Gate Driver Design in Progress

## **Next Steps**

- Phase I Tasks

- V

- Device Module Simulations

- Packaging Simulations

- Gate Driver Design

- Define Manufacturing Concept

- Epitaxial Growth of 6.5 kV JFET and JBS material

- Device Fabrication

- Module Assembly

- Half-Bridge Module Demonstration with Princeton power Systems

- Target: Alpha prototype by end of phase II (TRL 6)

**USCi's New SiC Epitaxial Growth Facility**

**USCi's Class 100 Pilot Wafer Fab**

## Conclusions

- United Silicon Carbide is proposing a <u>tractable</u> approach to developing a

6.5 kV medium voltage half-bridge switch module

- Will enable a 5 kV DC-Link voltage which will greatly impact Storage Systems by reducing costs of power conversion stages

- Impact current system designs as well as create a platform for highly innovative inverter/converter designs

- Module is based on an all SiC half-bridge module

- Utilizes Vertical JFETs and JBS's

- Focusing on reliability aspects of SiC materials

- All N-type SiC material system

- No MOS–Gate material

- Currently in Phase I

- Device Simulations Completed

- Current Efforts focused on Epitaxial Growth of 6.5 kV material

### Thank You!

**USCi Welcomes Your Questions**

PI: Dr. John L. Hostetler

Director of Epitaxial Growth

United Silicon Carbide

jhostetler@unitedsic.com

732-355-0550