# 6.5 KV SILICON CARBIDE ENHANCED MODE JFETS FOR HIGH VOLTAGE DC LINK APPLICATIONS

John Hostetler<sup>1</sup>, Peter Alexandrov<sup>1</sup>, Xueqing Li<sup>1</sup>, Leonid Fursin<sup>1</sup>, Anup Bhalla<sup>1</sup>, Martin Becker<sup>2</sup>, Frank Hoffman<sup>2</sup>, Jerry Sherbondy<sup>3</sup>, Don Morozowich<sup>3</sup>

<sup>1</sup>United Silicon Carbide, Inc., 7 Deer Park Drive, Monmouth Junction, NJ 08852,

<sup>2</sup>Princeton Power Systems, 3175 Princeton Pike, Lawrenceville, NJ 08648,

<sup>3</sup>Powerex, 173 Pavilion Lane, Youngwood, PA 15697

#### INTRODUCTION

- The excellent material properties of **silicon carbide (SiC)** semiconductors offer great promise for increasing the DC link voltage to well over 1 kV, while maintaining **high efficiency** and also achieving smaller more cost effective power conversion through faster switching.

- The ability to increase the DC-link voltage up to 4 kV per switch level, is an application especially attractive for SiC unipolar devices, for example, a JFET or MOSFET rated at 6.5 kV, could easily accommodate such operational voltages, while maintaining high switching speeds of 20 kHz.

- Unipolar SiC JFETs can enable small, lightweight, transformerless topologies for industrial medium voltage grid applications operating in the 3.3 kVAC or 4.16 kVAC regimes.

#### 6.5 kV SiC JFET PERFORMANCE

- SiC JFETs have demonstrated robust reliability over that of SiC-MOS technologies.

- SiC JFETs have the added advantage of reliable operation at T<sub>amb</sub> > 300°C, limited only by packaging.

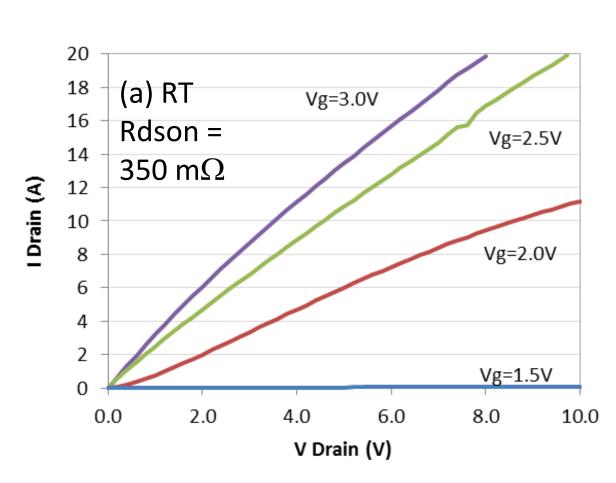

Fig. 1 USCi's Enhanced mode 6.5 kV SiC JFET forward conduction (a), and drain leakage showing ~7 kV blocking (b).

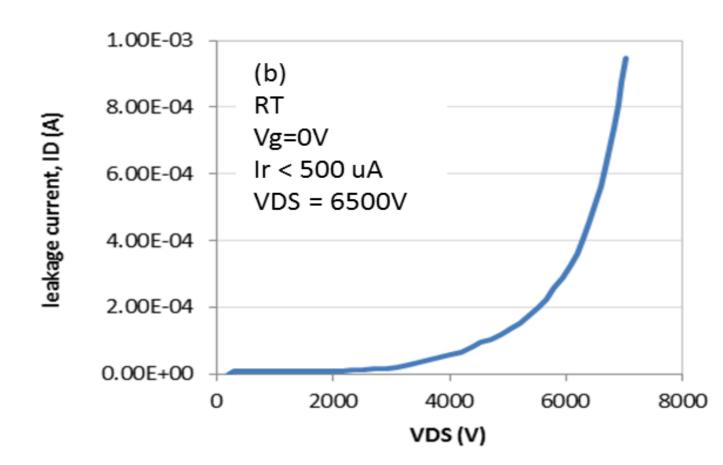

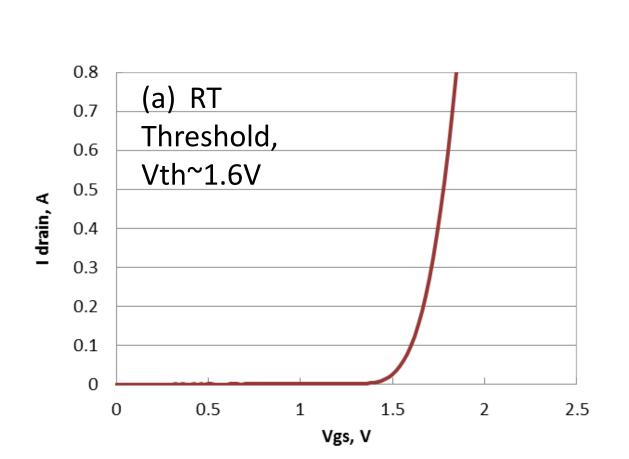

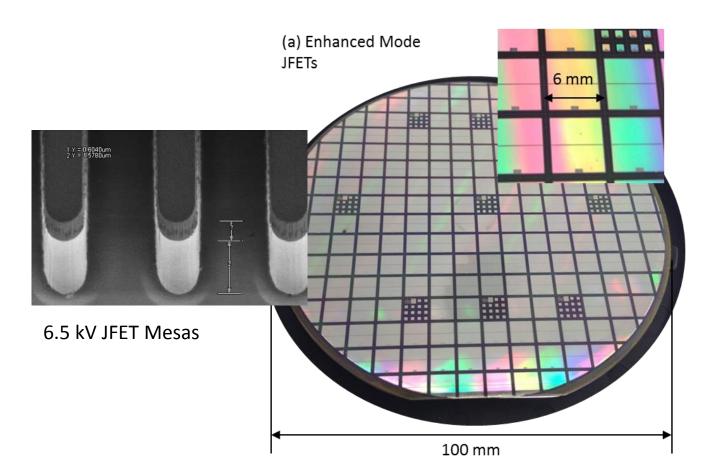

Fig. 2 SiC JFET Drain current vs. Gate-Source Voltage (a), and image of processed wafer showing Source mesas & large 6 x 6 mm die size (b).

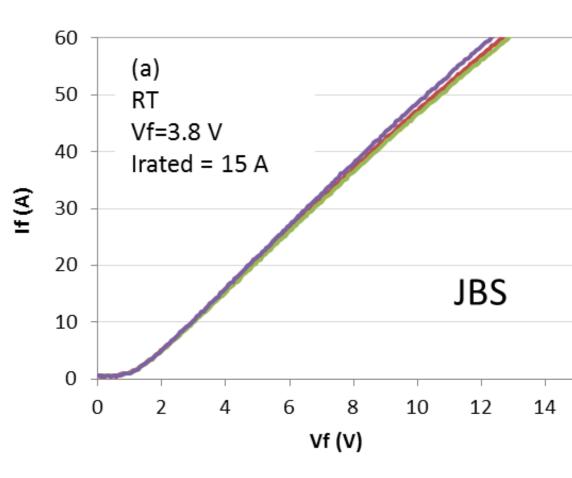

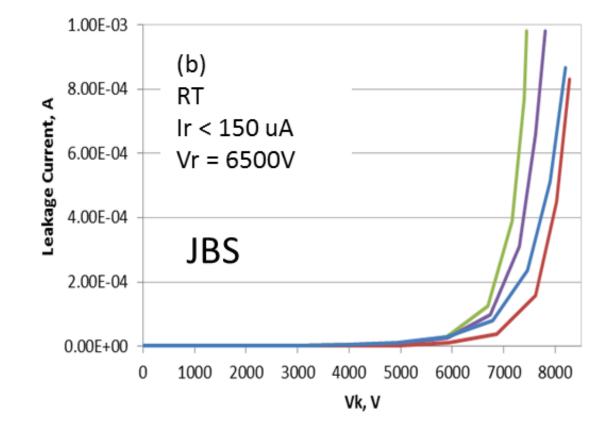

## 6.5 KV SiC DIODE PERFORMANCE

SiC Diodes offer near zero Qrr, (reverse recovery losses) and demonstrate excellent high current operation

Fig. 3 USCi's 6.5 kV SiC JBS Diode forward conduction (a), and cathode leakage showing >7 kV blocking (b).

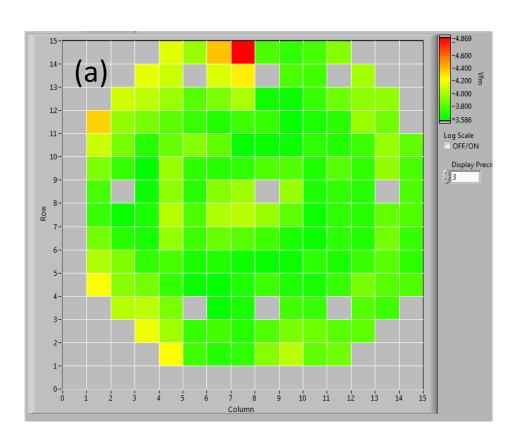

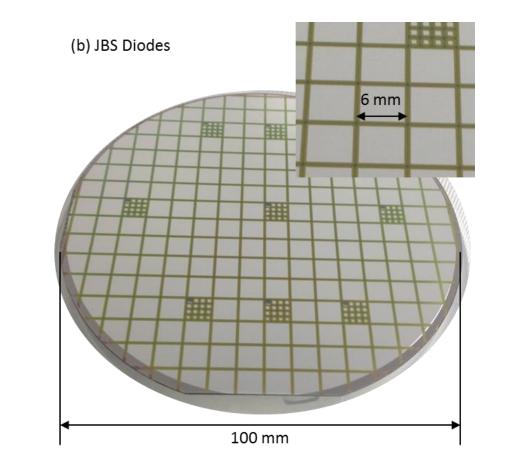

Fig. 4 RDS(on) map showing high yield on 100 mm wafer (a) and image of processed wafer showing large 6 x 6 mm die size (b).

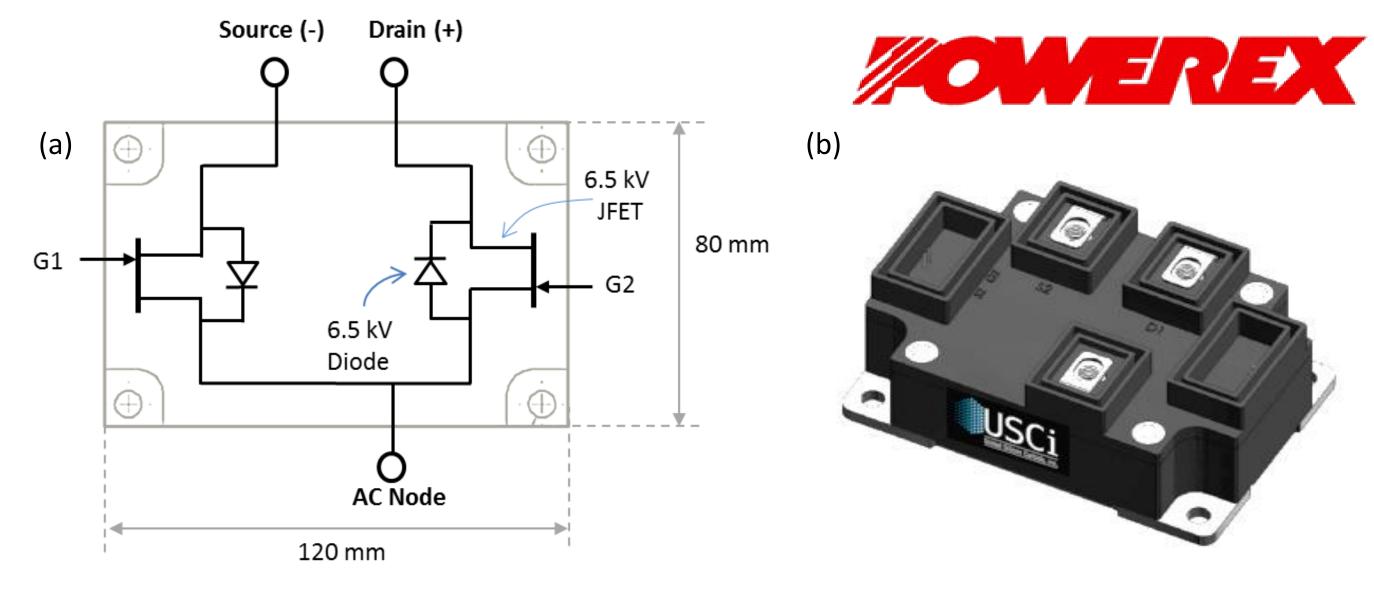

### 6.5 kV JFET POWER HALF-BRIDGE MODULE

■ The normally—off 6.5 kV JFETs will be assembled with the 6.5 kV Diodes in antiparallel to form a 20 kHz half-bridge power module rated with the following parmeters:

| Parameter                  | Symbol                                 | Value     | Units |  |

|----------------------------|----------------------------------------|-----------|-------|--|

| Drain-Source Voltage       | $V_{DS}$                               | 6500      | V     |  |

| Gate-Source Voltage        | $V_{GS}$                               | -20 to 20 | V     |  |

| Continuous Drain Current   | I <sub>D</sub> , T <sub>j</sub> =25°C  | 60        | А     |  |

|                            | I <sub>D</sub> , T <sub>j</sub> =125°C | 39        | А     |  |

| Pulsed Drain Current       | I <sub>D,pulsed</sub>                  | 120       | А     |  |

| Max Operation Temperature  | T <sub>j</sub>                         | 200       | °C    |  |

| Isolation Voltage          | V <sub>ISO</sub>                       | 10        | kV    |  |

| Drain Source On-Resistance | R <sub>DS(on)</sub>                    | 150       | mΩ    |  |

Fig. 5 Schematic of half-bridge power module (a) and final module design (b).

## 6.5 kV JFET MODULE APPLICATION

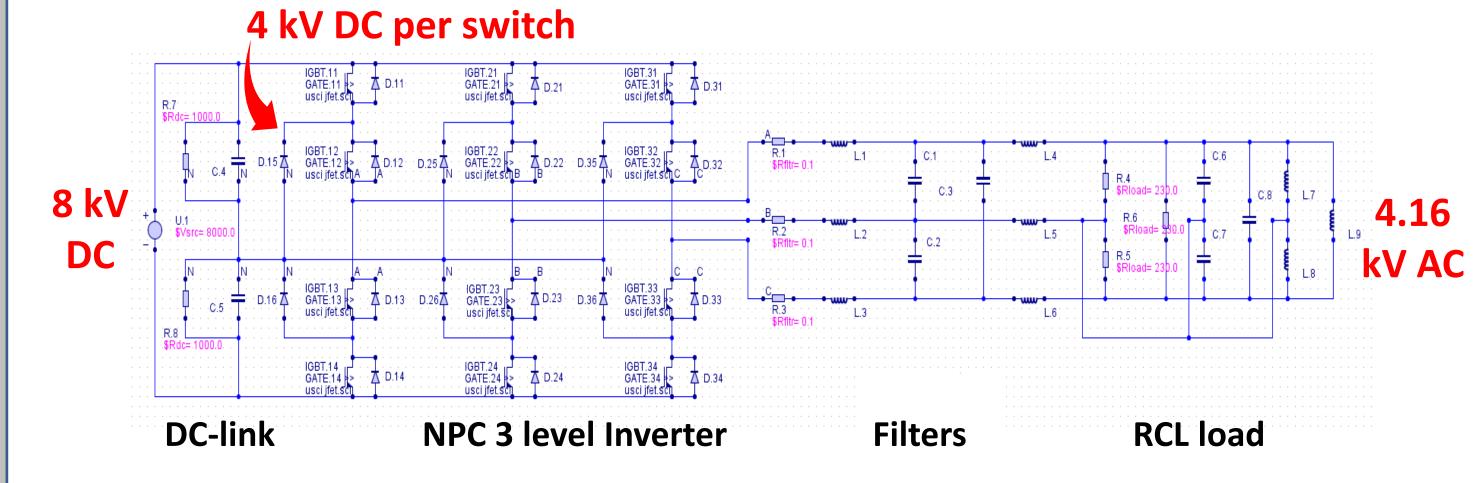

■ CASE STUDY: Simulation of Neutral Point Clamped (NPC) inverter for transformerless gridtie to 4.16 kVAC using SiC-JFET half-bridge module.

Fig. 6 Three-level neutral point clamped inverter enabling a 8 kV DC link for direct tie into an industrial distribution line at 4.16 kV AC

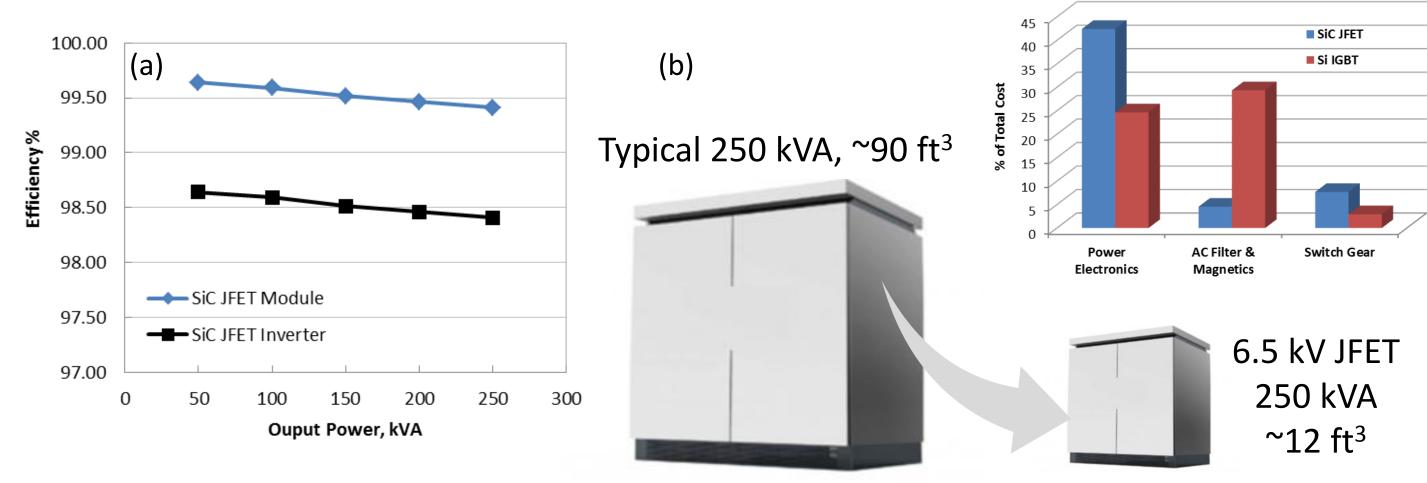

Fig. 7 Efficiency simulation of JFET modules and NPC inverter up to 250kVA output (a) and power density and cost benefit estimations on 250kVA inverter (b).

| Device<br>Platform        | Inverter<br>level | Inverter<br>Ouput<br>(kVA) | Max<br>Input<br>Voltage<br>(kV) | Typ Freq.<br>(kHz) | Efficiency<br>(%) | Size (ft <sup>3</sup> ) | Power<br>Density,<br>(MW/m³) | \$/W    | Comment                               |

|---------------------------|-------------------|----------------------------|---------------------------------|--------------------|-------------------|-------------------------|------------------------------|---------|---------------------------------------|

| Typical<br>1.2 kV Si IGBT | 2                 | 250                        | 1                               | 10                 | 96.0              | 90                      | 0.10                         | \$ 0.40 | Transformer included for 4.16 kV grid |

| NPC<br>6.5 kV SiC JFET    | 3                 | 250                        | 8                               | 20                 | 98.5              | 12                      | 0.75                         | \$ 0.36 | Transformerless to 4.16 kV grid       |

## Summary

- 6.5 kV SiC JFET and JBS Diode devices were fabricated for assembly and testing in half-bridge modules rated at 60 A, 20 kHz, and T<sub>amb</sub> = 200°C operation.

- Higher DC-link voltage capabilities enable next generation transformerless topologies.

- USCi would like to thank Dr. Imre Gyuk of the DOE Energy Storage Program for funding and Dr. Stan Atcitty of Sandia National Labs for his technical contribution.

- Sandia National Laboratories is a multi-program laboratory managed and operated by Sandia Corporation, a wholly owned subsidiary of Lockheed Martin Corporation, for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-AC04-94AL85000