## FRAUNHOFER CENTER FOR SILICION PHOTOVOLTAICS CSP

# EXPERIENCES ON PID TESTING OF PV MODULES IN 2012

### Sascha Dietrich, Jens Froebel, Matthias Ebert, Joerg Bagdahn

Fraunhofer - Center for Silicon-Photovoltaics CSP Walter-Huelse-Straße 1, 06120 Halle (Saale) Telefon +49 (0) 345/5589-408 sascha.dietrich@csp.fraunhofer.de

#### **Motivation**

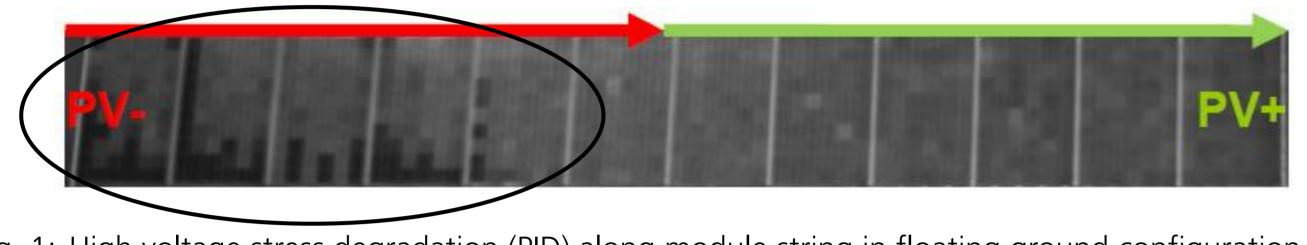

High voltage stress conditions are identified as a crucial degradation problem for solar cells

#### Results

test setup guides degradation pattern (Fig. 8)

- Degradation usually happens quickly (months), large scale and with high magnitude in terms of performance loss

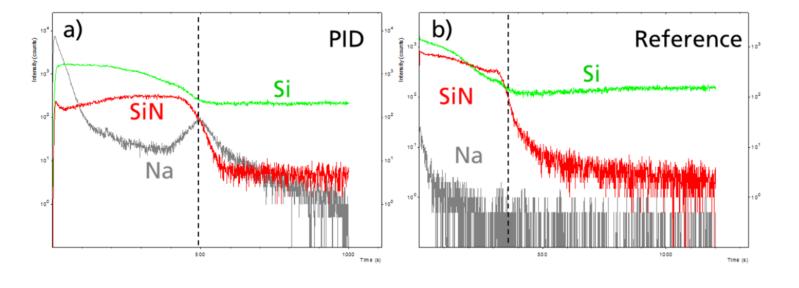

- Na+ migration through encapsulant and SiN due to potential between the cell and the frame + glass found as root cause

- Type approval test for modules required (IEC NWIP 62804)

Fig. 1: High voltage stress degradation (PID) along module string in floating ground configuration [1]

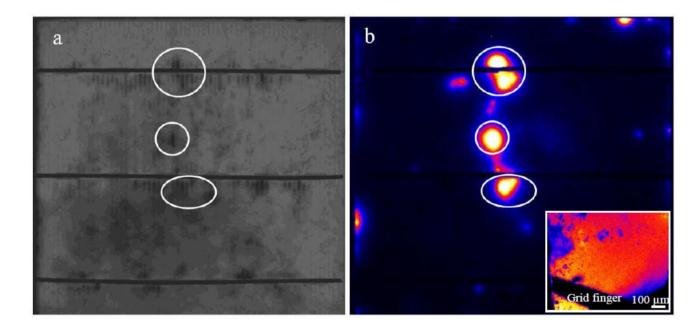

Fig. 2: Shunted regions on solar cell EL-image (left), LIT image (right) [2]

Fig. 3: Na accumulation at SiN / Si interface PID cell (left), reference cell (right) [2]

#### High Voltage Stress Testing (HVST)

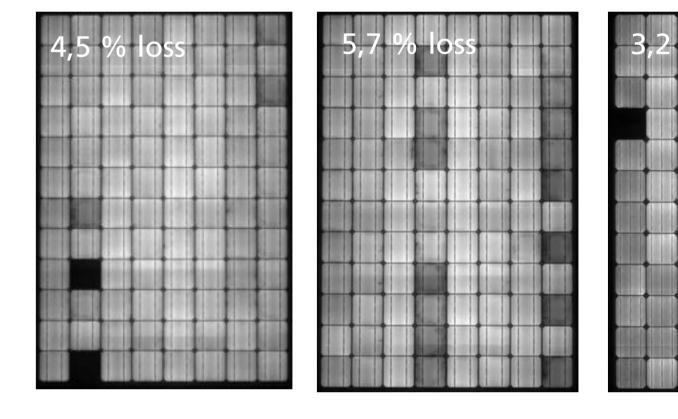

without Al-foil: strong concentration along the perimeter of the module

- with Al-foil: homogeneous electrode across module surface

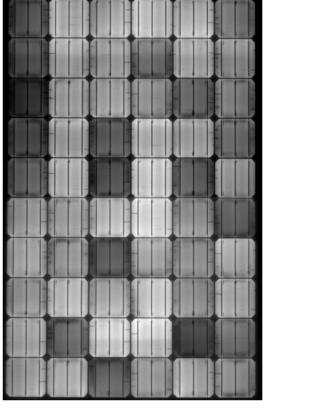

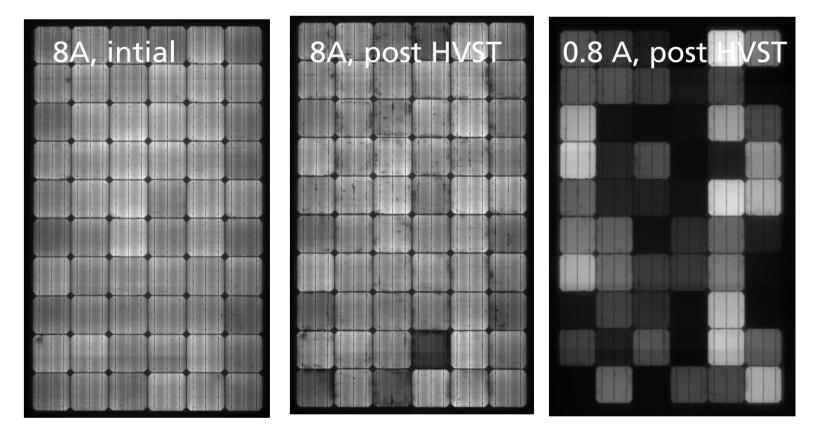

- A few degraded cells may lead to high degradation (Fig. 9)

- cells may be arbitrarily distributed across the module

- cloudy EL-image (local shunting) of a cell typically beginning of degradation

#### Discussion:

- statistical significance of HVST should be discussed  $\rightarrow$  needle in a haystack may be crucial to the result

- Iow current EL appropriate for qualitative statistical evaluation of progress of degradation

Fig. 8: Typical degradation pattern for different test approaches; left: setup 1; right: setup2

Fig. 9: Example where a few degraded cells with arbitrary distribution lead to rel. high performance los (8 A)

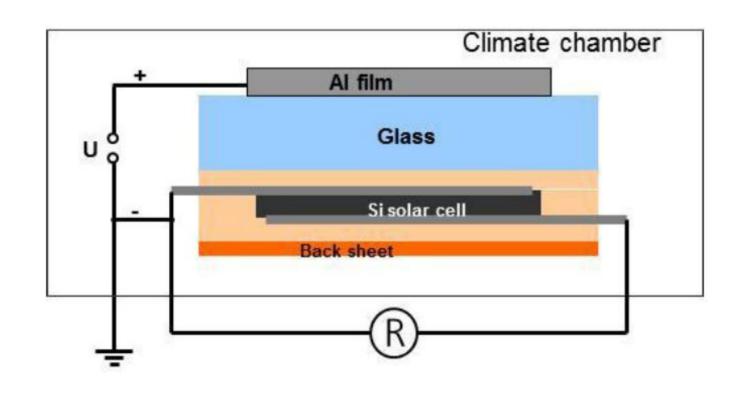

| Condition             | Setup 1 | Setup 2 | Setup 3 |

|-----------------------|---------|---------|---------|

| Relative Humidity     | 50 %    | 85 %    | 50 %    |

| Temperature           | 50 °C   | 60 °C   | 25 °C   |

| Al-foil               | yes     | no      | yes     |

| Test Duration         | 48 h    | 96 h    | 168 h   |

| No. of Modules Tested | 77      | 11      | 7       |

Fig. 4: Scheme of experimental setup 1

Fig. 5: Experimental setup 1 at Fraunhofer CSP with Al-foil covered PVC sheets

#### Results

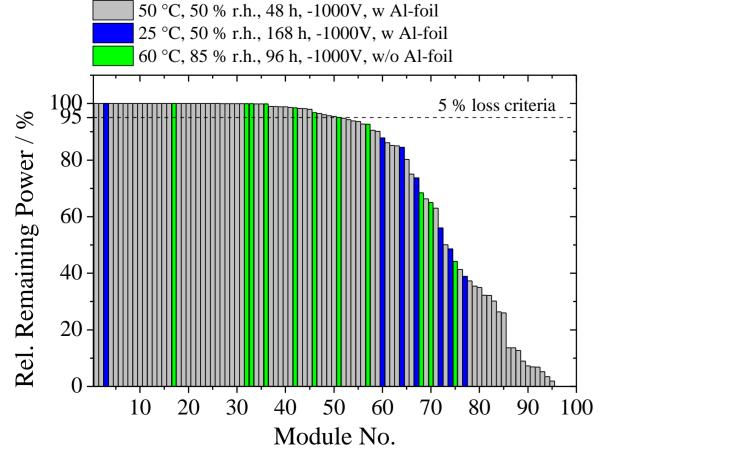

#### 46 % of modules failed the 5 % loss criteria (Fig. 6)

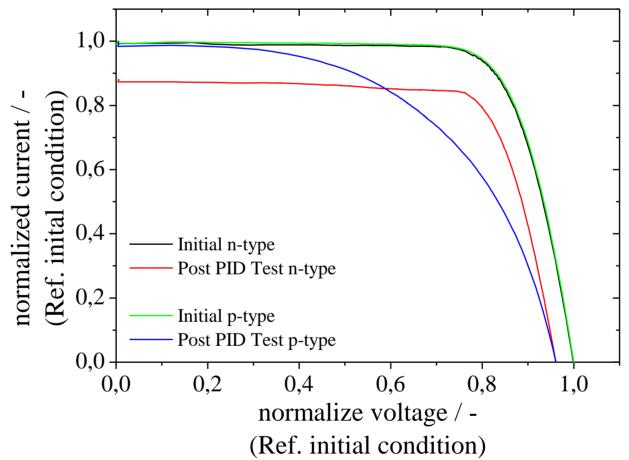

Fig. 10: Typical IV-curves for degraded n-type and p-type modules at -1000 V

Fig. 11: Local shunting of solar cells leads to cloudy EL image of cells (here: power loss 15 %)

#### Recovery

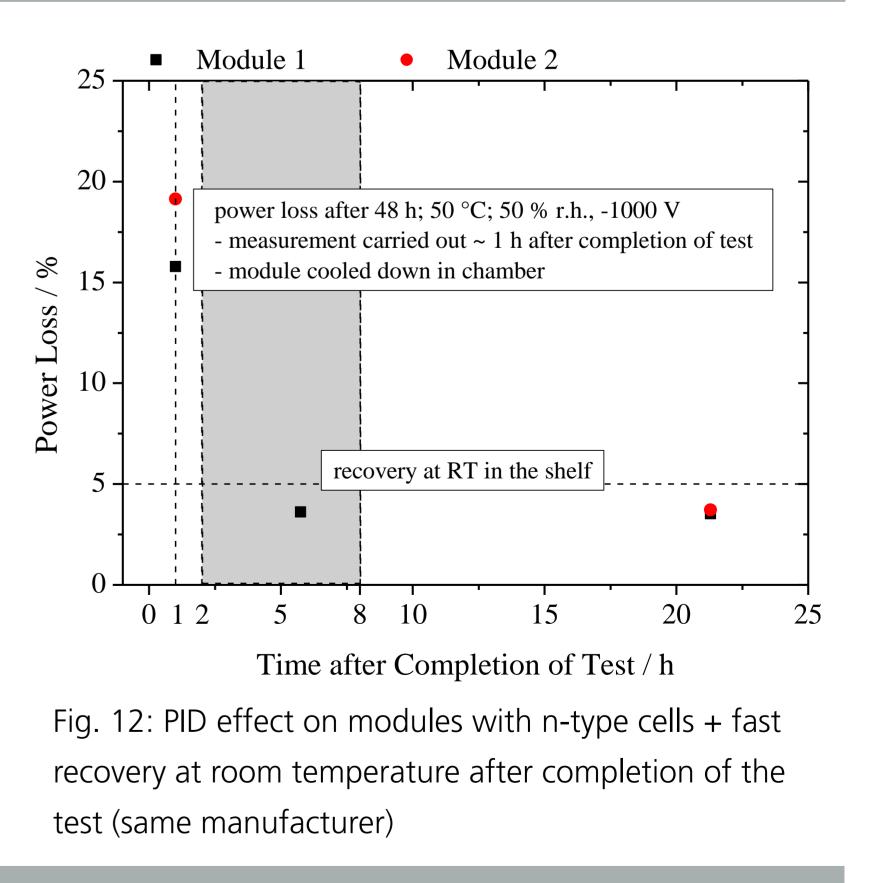

- n-type cells show PID effect at negative bias with different degradation characteristic compared to p-type cells

- fast recovery after testing

#### **Discussion**:

How to deal with this type of behavior in terms of testing?

scattering of power loss per module type can be very largely (Fig. 7)  $\rightarrow$  statistical scattering of PID sensitive cells

Fig. 6: Remaining power summarized for all tested modules (95 tested modules)

Manufacturer 1

Manufacturer 2 \* Manufacturer 3 100 5 % loss % criteria Rel. Remaining Power / 80 60 40 20 Product Type for each Manufacturer

Fig. 7: Rel. remaining power per product type of

several manufacturers (test setup 1)

Definition of time frame for characterization after HVST?

e.g. Minimum waiting time before measurement

Does it come with fast degradation during HVST?

#### **Bibliography**

[1] S. Pingel et al., "Potential Induced Degradation of Solar Cells and Panels," 35th IEEE PVSC, Honolulu, 2010, pp. 2817–2822.

V. Naumann, C. Hagendorf, S. Grosser, M. Werner, J. Bagdahn "Micro Structural [2] Root Cause Analysis of Potential Induced Degradation in c-Si Solar Cells" Energy Procedia, 27, 1 – 6 (2012)